EPM7192GI160-20

EE PLD, 20ns, CMOS, CPGA160Manufacturer: Altera

Categories: Programmable Logic Devices

Quality Control: Learn More

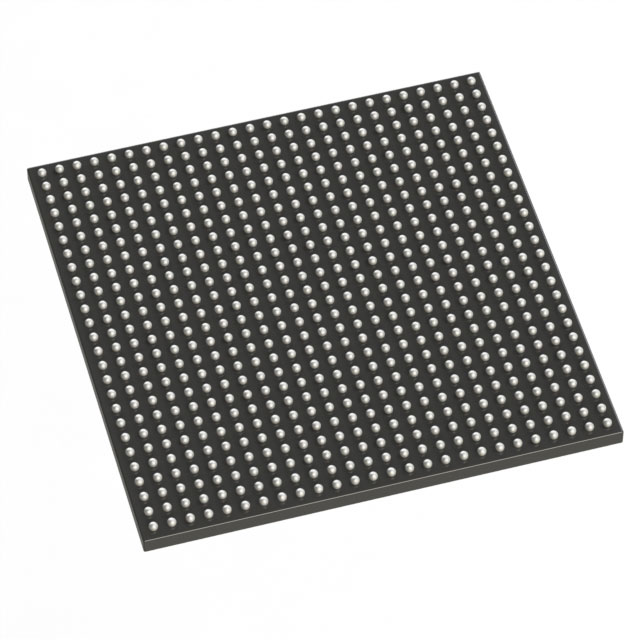

The Altera EPM7192GI160-20 is a high-density EE PLD from the EPM7192 series, featuring 192 macrocells with shared input/clock capabilities. This CMOS device operates with a maximum clock frequency of 62.5 MHz and a propagation delay of 20 ns, supporting a nominal supply voltage of 5V (4.5V to 5.5V). It is housed in a 160-terminal Ceramic Pin Grid Array (CPGA) package with a 2.54 mm terminal pitch. The device offers 120 I/O lines and is designed for demanding applications across industrial, telecommunications, and consumer electronics sectors. Its robust construction and established architecture make it suitable for complex logic designs requiring reliable performance within an operating temperature range of -40°C to 85°C.

Additional Information

Series: EPM7192RoHS Status: Manufacturer Lead Time: Product Status: DiscontinuedPackaging: Datasheet:Technical Details:

| Width | 39.6240 |

| Technology | CMOS |

| Length | 39.6240 |

| Additional_Feature | 192 MACROCELLS; SHARED INPUT/CLOCK |

| Clock_Frequency_Max | 62.50000 |

| JESD_30_Code | S-CPGA-P160 |

| Number_of_Dedicated_Inputs | 0 |

| Number_of_I_O_Lines | 120 |

| Number_of_Terminals | 160 |

| Operating_Temperature_Max | 85.0 |

| Operating_Temperature_Min | -40.0 |

| Organization | 0 DEDICATED INPUTS, 120 I/O |

| Output_Function | MACROCELL |

| Package_Body_Material | CERAMIC, METAL-SEALED COFIRED |

| Package_Code | PGA |

| Package_Shape | Square |

| Package_Style | GRID ARRAY |

| Programmable_Logic_Type | EE PLD |

| Propagation_Delay | 20.000 |

| Seated_Height_Max | 5.3400 |

| Supply_Voltage_Max | 5.50000 |

| Supply_Voltage_Min | 4.50000 |

| Supply_Voltage_Nom | 5 |

| Surface_Mount | No |

| Terminal_Form | PIN/PEG |

| Terminal_Pitch | 2.540 |

| Terminal_Position | Perpendicular |