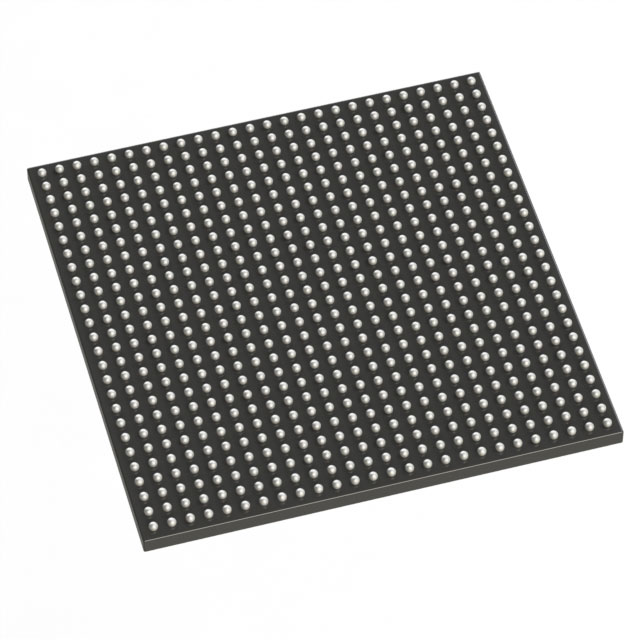

EPM7192EGM160-20

EE PLD, 20ns, 192-Cell, CMOS, CPGA160Manufacturer: Altera

Categories: Programmable Logic Devices

Quality Control: Learn More

Altera EPM7192 EE PLD, part number EPM7192EGM160-20, offers 192 macrocells and a 20ns propagation delay. This CMOS device features configurable I/O operation supporting 3.3V or 5V, along with two external clocks and shared input/clock capabilities. Designed with 120 I/O lines within a 160-terminal PGA package, it operates over an industrial temperature range of -55°C to 125°C. The EPM7192 series is utilized in applications requiring high-speed logic implementation, including telecommunications, industrial control, and data processing systems. The ceramic, metal-sealed cofired package ensures robust performance in demanding environments.

Additional Information

Series: EPM7192RoHS Status: Manufacturer Lead Time: Product Status: DiscontinuedPackaging: Datasheet:Technical Details:

| Length | 39.6240 |

| Width | 39.6240 |

| Technology | CMOS |

| Additional_Feature | 192 MACROCELLS; CONFIGURABLE I/O OPERATION (3.3V OR 5V); 2 EXTERNAL CLOCKS; SHARED INPUT/CLOCK |

| Clock_Frequency_Max | 62.50000 |

| In_System_Programmable | No |

| JESD_30_Code | S-CPGA-P160 |

| JTAG_BST | No |

| Number_of_Dedicated_Inputs | 0 |

| Number_of_I_O_Lines | 120 |

| Number_of_Inputs | 124 |

| Number_of_Macro_Cells | 192 |

| Number_of_Outputs | 120 |

| Number_of_Terminals | 160 |

| Operating_Temperature_Max | 125.0 |

| Operating_Temperature_Min | -55.0 |

| Organization | 0 DEDICATED INPUTS, 120 I/O |

| Output_Function | MACROCELL |

| Package_Body_Material | CERAMIC, METAL-SEALED COFIRED |

| Package_Code | PGA |

| Package_Equivalence_Code | PGA160M,15X15 |

| Package_Shape | Square |

| Package_Style | GRID ARRAY |

| Programmable_Logic_Type | EE PLD |

| Propagation_Delay | 20.000 |

| Seated_Height_Max | 5.3400 |

| Supply_Voltage_Max | 5.50000 |

| Supply_Voltage_Min | 4.50000 |

| Supply_Voltage_Nom | 5 |

| Surface_Mount | No |

| Terminal_Form | PIN/PEG |

| Terminal_Pitch | 2.540 |

| Terminal_Position | Perpendicular |