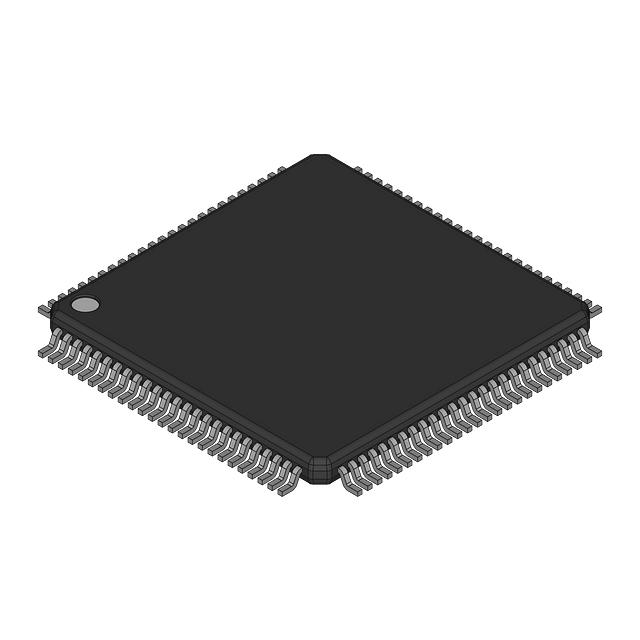

EPM7064SLC68-10

EE PLD, 10ns, 64-Cell, CMOS, PQCC68Manufacturer: Altera

Categories: Programmable Logic Devices

Quality Control: Learn More

Altera EPM7064 series EE PLD, part number EPM7064SLC68-10, offers a 64-macrocell count within a 10ns propagation delay. This CMOS device operates from a 4.75V to 5.25V supply range, with configurable I/O supporting 3.3V or 5V operation. Featuring 48 I/O lines and a total of 68 terminals, it is housed in a J-lead square chip carrier package (PQCC68). The EPM7064SLC68-10 is in-system programmable and finds application in telecommunications, industrial control, and consumer electronics. Its maximum clock frequency is 100 MHz.

Additional Information

Series: EPM7064RoHS Status: Manufacturer Lead Time: Product Status: DiscontinuedPackaging: Datasheet:Technical Details:

| Width | 24.2300 |

| Technology | CMOS |

| Length | 24.2300 |

| Additional_Feature | CONFIGURABLE I/O OPERATION WITH 3.3V OR 5V |

| Clock_Frequency_Max | 100.00000 |

| In_System_Programmable | Yes |

| JESD_30_Code | S-PQCC-J68 |

| JTAG_BST | No |

| Number_of_Dedicated_Inputs | 0 |

| Number_of_I_O_Lines | 48 |

| Number_of_Macro_Cells | 64 |

| Number_of_Terminals | 68 |

| Operating_Temperature_Max | 70.0 |

| Operating_Temperature_Min | 0.0 |

| Organization | 0 DEDICATED INPUTS, 48 I/O |

| Output_Function | MACROCELL |

| Package_Body_Material | PLASTIC/EPOXY |

| Package_Code | QCCJ |

| Package_Equivalence_Code | LDCC68,1.0SQ |

| Package_Shape | Square |

| Package_Style | CHIP CARRIER |

| Programmable_Logic_Type | EE PLD |

| Propagation_Delay | 10.000 |

| Seated_Height_Max | 5.0800 |

| Supply_Voltage_Max | 5.25000 |

| Supply_Voltage_Min | 4.75000 |

| Supply_Voltage_Nom | 5 |

| Surface_Mount | Yes |

| Terminal_Form | J BEND |

| Terminal_Pitch | 1.270 |

| Terminal_Position | QUAD |