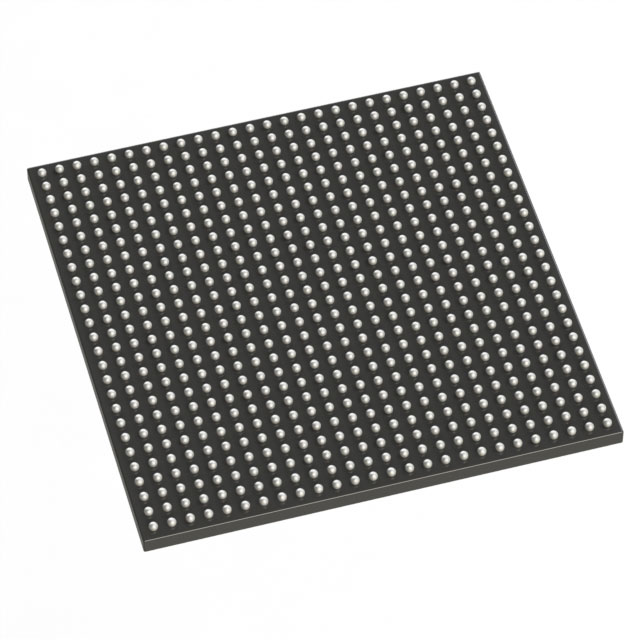

EPF10K100BM560-5

Loadable PLD, 27ns, CMOS, PBGA560Manufacturer: Altera

Categories: Programmable Logic Devices

Quality Control: Learn More

Altera EPF10K100BM560-5 is a loadable PLD featuring 4992 configurable logic elements and 560 terminals in a square, bottom-entry, ball grid array (PBGA560) package. This CMOS device operates with configurable I/O supporting 3.3V or 5V, and a nominal supply voltage of 5V, ranging from 4.5V to 5.5V. It boasts a maximum clock frequency of 53.76 MHz and a propagation delay of 27 ns. The component offers 4 dedicated inputs and registered output functions. Its operating temperature range spans from -55°C to 125°C. Applications for this Altera device include telecommunications, industrial control, and computing systems.

Additional Information

Series: EPF10K100RoHS Status: Manufacturer Lead Time: Product Status: DiscontinuedPackaging: Datasheet:Technical Details:

| Length | 42.5000 |

| Width | 42.5000 |

| Technology | CMOS |

| Additional_Feature | 4992 LOGIC ELEMENTS CONFIGURABLE I/O OPERATION WITH 3.3V OR 5V |

| Clock_Frequency_Max | 53.76000 |

| JESD_30_Code | S-PBGA-B560 |

| Number_of_Dedicated_Inputs | 4 |

| Number_of_Terminals | 560 |

| Operating_Temperature_Max | 125.0 |

| Operating_Temperature_Min | -55.0 |

| Organization | 4 DEDICATED INPUTS |

| Output_Function | REGISTERED |

| Package_Body_Material | PLASTIC/EPOXY |

| Package_Code | BGA |

| Package_Shape | Square |

| Package_Style | GRID ARRAY |

| Programmable_Logic_Type | LOADABLE PLD |

| Propagation_Delay | 27.000 |

| Seated_Height_Max | 1.7000 |

| Supply_Voltage_Max | 5.50000 |

| Supply_Voltage_Min | 4.50000 |

| Supply_Voltage_Nom | 5 |

| Surface_Mount | Yes |

| Terminal_Form | Ball |

| Terminal_Pitch | 1.270 |

| Terminal_Position | Bottom |